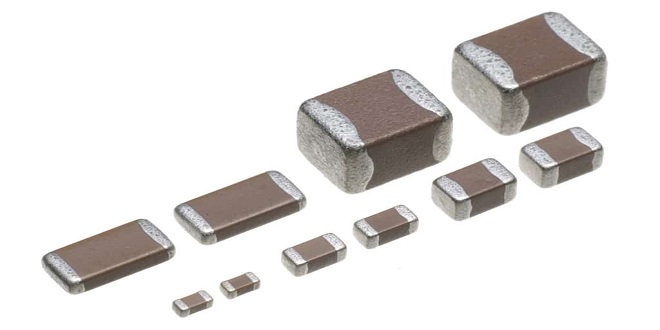

AEC-Q200 Low Inductance Ceramic Capacitors (LICC)

The signal integrity characteristics of a Power Delivery Network (PDN) are becoming critical aspects of board level and semiconductor package designs due to higher operating frequencies, larger power demands, and the ever shrinking lower and upper voltage limits around low operating voltages. These power system challenges are coming from mainstream designs with operating frequencies of 300MHz or greater, modest ICs with power demand of 15 watts or more, and operating voltages below 3 volts.

The classic PDN topology is comprised of a series of capacitor stages. Figure 1 is an example of this architecture with multiple capacitor stages

LOW INDUCTANCE CHIP CAPACITORS

The key physical characteristic determining equivalent series inductance (ESL) of a capacitor is the size of the current loop it creates. The smaller the current loop, the lower the ESL. A standard surface mount MLCC is rectangular in shape with electrical terminations on its shorter sides. A Low Inductance Chip Capacitor (LICC) sometimes referred to as Reverse Geometry Capacitor (RGC) has its terminations on the longer side of its rectangular shape

INTERDIGITATED CAPACITORS

The size of a current loop has the greatest impact on the ESL characteristics of a surface mount capacitor. There is a secondary method for decreasing the ESL of a capacitor. This secondary method uses adjacent opposing current loops to reduce ESL. The InterDigitated Capacitor (IDC) utilizes both primary and secondary methods of reducing inductance. The IDC architecture shrinks the distance between terminations to minimize the current loop size, then further reduces inductance by creating adjacent opposing current loops.

LAND GRID ARRAY (LGA) CAPACITORS

Land Grid Array (LGA) capacitors are based on the first Low ESL MLCC technology created to specifically address the design needs of current day Power Delivery Networks (PDNs). This is the 3rd low inductance capacitor technology developed by AVX. LGA technology provides engineers with new options. The LGA internal structure and manufacturing technology eliminates the historic need for a device to be physically small to create small current loops to minimize inductance.

LOW INDUCTANCE CHIP ARRAYS (LICA)

The LICA product family is the result of a joint development effort between AVX and IBM to develop a high performance MLCC family of decoupling capacitors. LICA was introduced in the 1980s and remains the leading choice of designers in high performance semiconductor packages and high reliability board level decoupling applications

GENERAL DESCRIPTION

The key physical characteristic determining equivalent series inductance (ESL) of a capacitor is the size of the current loop it creates. The smaller the current loop, the lower the ESL. A standard surface mount MLCC is rectangular in shape with electrical terminations on its shorter sides. A Low Inductance Chip Capacitor (LICC) sometimes referred to as Reverse Geometry Capacitor (RGC) has its terminations on the longer sides of its rectangular shape.

The image on the right shows the termination differences between an MLCC and an LICC. When the distance between terminations is reduced, the size of the current loop is reduced. Since the size of the current loop is the primary driver of inductance, an 0306 with a smaller current loop has significantly lower ESL then an 0603. The reduction in ESL varies by EIA size, however, ESL is typically reduced 60% or more with an LICC versus a standard MLCC. AVX LICC products are now qualified to AEC-Q200 for automotive applications.

The fury of nature can be seen in the formation and power of tornadoes. These violent storms can cause immense destruction, but with proper preparation, it is possible to survive the storm. Tornadoes form when warm, moist air meets cold, dry air, creating a powerful rotating vortex. The power of a tornado is measured on the Enhanced Fujita Scale, which ranges from EF0 to EF5, with EF5 tornadoes being the most devastating. Surviving a tornado involves seeking shelter in a sturdy building or underground, away from windows and exterior walls. It is crucial to have a preparedness plan and to stay informed about severe weather warnings. By understanding the formation and power of tornadoes, individuals can take the necessary steps to stay safe when these storms strike.